# Lecture Notes in Computer Science

4415

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Paul Lukowicz Lothar Thiele Gerhard Tröster (Eds.)

# Architecture of Computing Systems - ARCS 2007

20th International Conference Zurich, Switzerland, March 12-15, 2007 Proceedings

#### Volume Editors

Paul Lukowicz University of Passau IT-Center/International House Innstraße 43, 94032 Passau, Germany E-mail: paul.lukowicz@uni-passau.de

#### Lothar Thiele

Swiss Federal Institute of Technology Zurich Computer Engineering and Networks Laboratory Gloriastrasse 35, 8092 Zurich, Switzerland

E-mail: thiele@tik.ee.ethz.ch

Gerhard Tröster Swiss Federal Institute of Technology Zurich Electronics Laboratory Gloriastrasse 35, 8092 Zürich. Switzerland E-mail: troester@ife.ee.ethz.ch

Library of Congress Control Number: 2007922097

CR Subject Classification (1998): C.2, C.5.3, D.4, D.2.11, H.3.5, H.4, H.5.2

LNCS Sublibrary: SL 1 – Theoretical Computer Science and General Issues

ISSN 0302-9743

ISBN-10 3-540-71267-4 Springer Berlin Heidelberg New York ISBN-13 978-3-540-71267-1 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2007 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12031580 06/3142 5 4 3 2 1 0

# **Preface**

The ARCS series of conferences has over 30 years of tradition reporting high-quality results in computer architecture and operating systems research. While the conference is proud of its long tradition, it is also proud to represent a dynamic, evolving community that closely follows new research trends and topics. Thus, over the last few years, ARCS has evolved towards a strong focus on system aspects of pervasive computing and self-organization techniques (organic and autonomic computing). At the same time it has expanded from its roots as a German Informatics Society (GI/ITG) conference to an international event. This is reflected by the composition of the TPC which included over 30 renown scientist from 10 different countries. The conference attracted 83 submission from 16 countries across 4 continents. Of those, 20 have been accepted, which amounts to an acceptance rate below 25%.

The 20th ARCS event was a special anniversary conference. It is only fitting that it was held at a special place: the ETH Zurich. It combines one of the leading information technology schools in Europe with a beautiful location.

I would like to express my gratitude to all those who made this year's conference possible. This includes the General Chairs Lothar Thiele and Gerhard Tröster from ETH, the Tutorials and Workshops Chair Marco Platzner from the University of Paderborn, the members of the "Fachausschus ARCS" of the GI/ITG (the Steering Committee), the members of the Technical Program Committee, the Reviewers, and most of all to all the authors that submitted their work to ARCS 2007. I would also like to thank IFIP, ITG/Electrosuisse, VDE and the ARTIST2 Project for their support of the conference.

January 2007 Paul Lukowicz

# Organization

# Organizing Committee

Conference Chairs: Lothar Thiele (ETH Zurich, Switzerland)

Gerhard Tröster (ETH Zurich, Switzerland )

Program Chair: Paul Lukowicz (University of Passau, Germany)

Workshops and Tutorials: Marco Platzner (University of Paderborn, Germany)

# Program Committee

Nader Bagherzadeh, University of California, Irvine, USA

Michael Beigl, University of Braunschweig, Germany

Michael Berger, Siemens AG, Munich, Germany

Don Chiarulli, University of Pittsburgh, USA

Giovanni Demicheli, EPFL Lausanne, Switzerland

Koen De Bosschere, Ghent University, Belgium

Alois Ferscha, University of Linz, Austria

Mike Hazaas, Lancaster University, UK

Ernst Heinz, UMIT Hall i. Tirol, Austria

Paolo Ienne, EPFL Lausanne, Switzerland

Wolfgang Karl, University of Karlsruhe, Germany

Spyros Lalis, University of Thessaly, Greece

Koen Langendoen, Delft University of Technology, The Netherlands

Tom Martin, Virginia Tech, USA

Hermann de Meer, University of Passau, Germany

Erik Maehle, University of Luebeck, Germany

Peter Marwedel, University of Dortmund, Germany

Christian Mller-Schloer, University of Hanover, Germany

Stephane Vialle, Supelec, France

Joe Paradiso, MIT Media Lab, USA

Daniel Roggen, ETH Zurich, Switzerland

Pascal Sainrat, Université Paul Sabatier, Toulouse, France

Heiko Schuldt, University of Basel, Switzerland

Hartmut Schmeck, University of Karlsruhe, Germany

Karsten Schwan, Georgia Tech, Atlanta, USA

Bernhard Sick, University of Passau, Germany

Juergen Teich, University of Erlangen, Germany

Pedro Trancoso, University of Cyprus, Cyprus

Theo Ungerer, University of Augsburg, Germany

Stamatis Vassiliadis, Delft University of Technology, The Netherlands

Lucian Vintan, Lucian Blaga University of Sibiu, Romania

Klaus Waldschmidt, University of Frankfurt, Germany

#### Additional Reviewers

Henoc Agbota Mohammed Al-Loulah Muneeb Ali Ioannis Avramopoulos Congalo Bailador

Gonzalo Bailador David Bannach Juergen Becker Andrey Belenky Mladen Berekovic Uwe Brinkschulte Rainer Buchty

Georg Carle Supriyo Chatterjea Marcelo Cintra Philippe Clauss Joshua Edmison

Werner Erhard Philippe Faes Diego Federici Dietmar Fey

Mamoun Filali Amine Stefan Fischer Pierfrancesco Foglia Thomas Fuhrmann Martin Gaedke Marco Goenne

Werner Grass

Jan Haase

Erik Hagersten

Jörg Hähner

Gertjan Halkes

Holger Harms

Sabine Hauert

Wim Heirman

Jörg Henkel

Michael Hinchey

Alexander Hofmann

Ulrich Hofmann

Amir Kamalizad

Dimitrios Katsaros

Bernd Klauer Manfred Kunde Kai Kunze

Lei Liu

Christoph Langguth Marc Langheinrich Baochun Li

Paul Lokuciejewski Clemens Lombriser Thanasis Loukopoulos

Jonas Maebe Rene Mayrhofer Lotfi Mhamdi Jörg Mische Florian Moesch Thorsten Möller Katell Morin-Allory Sanaz Mostaghim Leyla Nazhandali

Pasquale Pagano Thomas Papakostas

Afshin Niktash

Hooman Parizi

Tom Parker

Neal Patwari

Andy Pimentel

Thilo Pionteck

Laura Pozzi

Robert Pyka

Markus Ramsauer

Thomas Schwarzfischer

Andr Seznec

Enrique Soriano

Ioannis Sourdis

Michael Springmann

Mathias Stäger

Yannis Stamatiou

Kyriakos Stavrou

Walter Stiehl

Mototaka Suzuki

Joseph Sventek

Jie Tao

Karl-Heinz Temme Sascha Uhrig Miljan Vuletic Jamie Ward Ralph Welge Lars Wolf Bernd Wolfinger Markus Wulff Olivier Zendra Peter Zipf

# **Table of Contents**

# **ARCS 2007**

| A Reconfigurable Processor for Forward Error Correction                                                                                   | 1   |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| FPGA-Accelerated Deletion-Tolerant Coding for Reliable Distributed Storage                                                                | 14  |

| LIRAC: Using Live Range Information to Optimize Memory Access<br>Peng Li, Dongsheng Wang, Haixia Wang, Meijuan Lu, and<br>Weimin Zheng    | 28  |

| Optimized Register Renaming Scheme for Stack-Based x86 Operations                                                                         | 43  |

| A Customized Cross-Bar for Data-Shuffling in Domain-Specific SIMD Processors                                                              | 57  |

| Customized Placement for High Performance Embedded Processor Caches                                                                       | 69  |

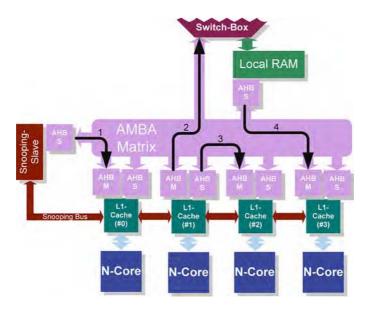

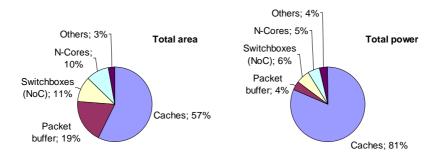

| A Multiprocessor Cache for Massively Parallel SoC Architectures Jörg-Christian Niemann, Christian Liβ, Mario Porrmann, and Ulrich Rückert | 83  |

| Improving Resource Discovery in the Arigatoni Overlay Network                                                                             | 98  |

| An Effective Multi-hop Broadcast in Vehicular Ad-Hoc Network                                                                              | 112 |

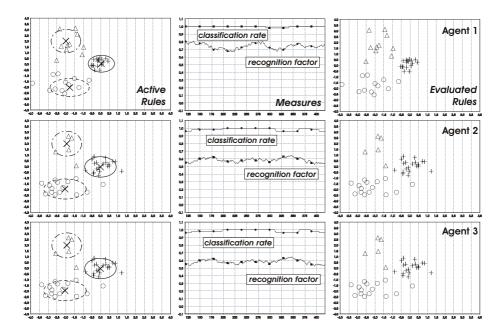

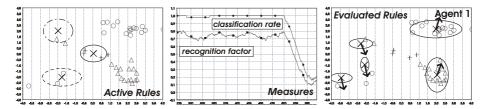

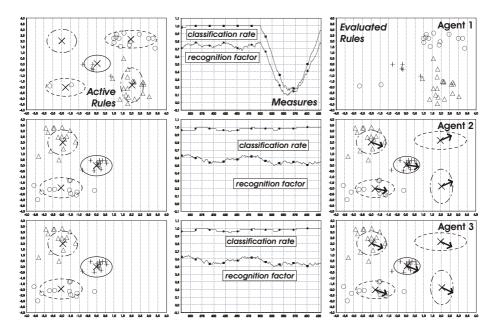

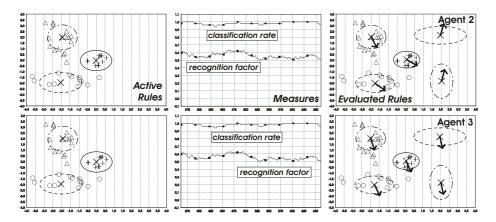

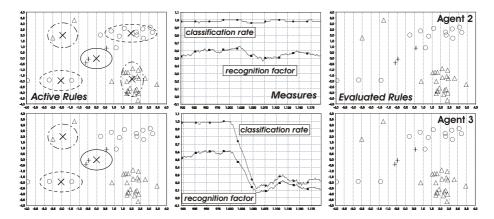

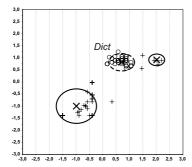

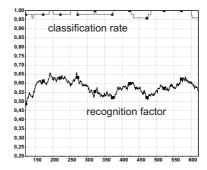

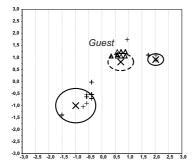

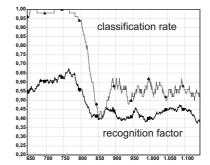

| Functional Knowledge Exchange Within an Intelligent Distributed System  Oliver Buchtala and Bernhard Sick                                 | 126 |

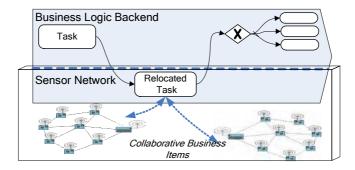

| Architecture for Collaborative Business Items                                                                                             | 142 |

# X Table of Contents

| Autonomic Management Architecture for Flexible Grid Services  Deployment Based on Policies  Edgar Magaña, Laurent Lefevre, and Joan Serrat | 157 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Variations and Evaluations of an Adaptive Accrual Failure Detector to Enable Self-healing Properties in Distributed Systems                | 171 |

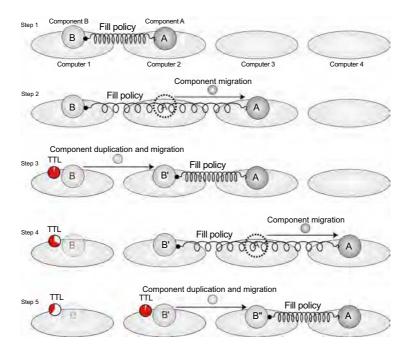

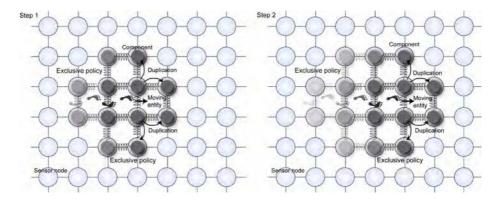

| Self-organizing Software Components in Distributed Systems                                                                                 | 185 |

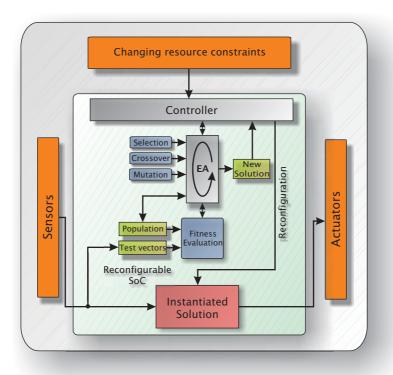

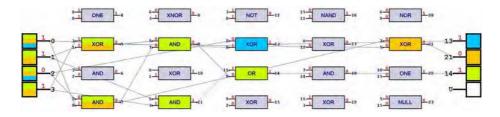

| Toward Self-adaptive Embedded Systems: Multi-objective Hardware Evolution                                                                  | 199 |

| Measurement and Control of Self-organised Behaviour in Robot Swarms                                                                        | 209 |

| Autonomous Learning of Load and Traffic Patterns to Improve Cluster Utilization                                                            | 224 |

| Parametric Architecture for Function Calculation Improvement                                                                               | 240 |

| Design Space Exploration of Media Processors: A Generic VLIW Architecture and a Parameterized Scheduler                                    | 254 |

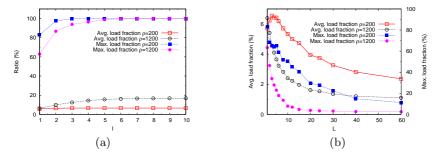

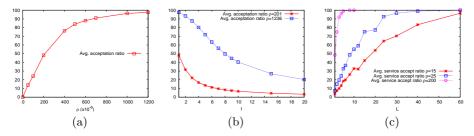

| Modeling of Interconnection Networks in Massively Parallel Processor Architectures                                                         | 268 |

| Invited Talk: Expanding Software Product Families: From Integration to Composition                                                         | 283 |

| Author Index                                                                                                                               | 297 |

# A Reconfigurable Processor for Forward Error Correction

Afshin Niktash, Hooman T. Parizi, and Nader Bagherzadeh

536 Engineering Tower, Henry Samueli School of Engineering, University of California, Irvine, CA 92697-2625, USA {aniktash,hparizi,nader}@ece.uci.edu

Abstract. In this paper, we introduced a reconfigurable processor optimized for implementation of Forward Error Correction (FEC) algorithms and provided the implementation results of the Viterbi and Turbo decoding algorithms. In this architecture, an array of processing elements is employed to perform the required operations in parallel. Each processing element encapsulates multiple functional units which are highly optimized for FEC algorithms. A data buffer coupled with high bandwidth interconnection network facilitates pumping the data to the array and collecting the results. A processing element controller orchestrates the operation and the data movement. Different FEC algorithms like Viterbi, Turbo, Reed-Solomon and LDPC are widely used in digital communication and could be implemented on this architecture. Unlike traditional approach to programmable FEC architectures, this architecture is instruction-level programmable which results the ultimate flexibility and programmability.

**Keywords:** Reconfigurable Processor, Processing Element, Forward Error Correction, Viterbi, Turbo.

#### 1 Introduction

Reconfigurable architectures customize the same piece of silicon for multiple applications. While general purpose processors could not meet the processing requirements of many new applications, traditional custom ASIC dominates the design space. In wireless communication, a DSP processor is usually responsible for low data rate signal processing and is coupled with customized silicon to perform the medium and high data rate processing. The main drawback of a custom design is its long and costly design cycle which requires high initial investment and results in long time-to-market. Furthermore, lack of flexibility and programmability of traditional solutions causes frequent design changes and tape-outs for emerging and developing standards. Reconfigurable architectures on the other hand are very flexibly and programmable and could significantly shorten the design cycle of new products while even extending the life cycle of existing products. Tracking new standards is simplified to software upgrades which could be performed on-the-fly.

One of the challenging applications of a reconfigurable architecture is channel coding. Almost any digital communication system benefits from at least one form of

error correction coding [1]. There are four main algorithms widely used in wireless and wired communications: Viterbi, Turbo, Reed-Solomon and LDPC. However, multiple variations of each of these algorithms are employed in standards. More specifically, every standard uses a different configuration of an algorithm which makes that unique to that standard. For example, , the Turbo code used in W-CDMA standard has a different polynomial, block size, rate and termination scheme from that used in WiMAX. Viterbi coding employed in W-LAN, W-CDMA and WiMAX are not the same. This translates to having a plurality of coding accelerators for different coding algorithms and configurations which is very common in industry. In conventional approach, a separate coprocessor is employed for every FEC algorithm. Nevertheless, even one coprocessor is not programmable enough to cover all existing configurations of an FEC algorithm for multiple standards.

In this paper, we introduce RECFEC, a REConfigurable processor optimized for Forward Error Correction algorithms. RECFEC combines the programmability of a DSP processor with performance of a dedicated hardware and is architected to enable effective software implementation of FEC algorithms. The organization of this paper is as follows. Section 2 reviews the related works. Section 3 describes the RECFEC architecture and programming model. Section 4 presents two examples of algorithm implementation, Viterbi and Turbo coding and Section 5 concludes the paper.

#### 2 Related Works

There are considerable research efforts to develop prototypes of reconfigurable architectures for channel coding. In this section, we present the features of those architectures.

A reconfigurable signal processor is introduced in [2] using an FPGA based reconfigurable processing board to implement a programmable Turbo decoder.

Viturbo[3] is among the first contributions trying to integrate Viterbi and Turbo decoders into a single architecture. Viturbo is a runtime reconfigurable architecture designed and implemented on an FPGA. The architecture can be reconfigured to decode a range of convolutionally coded data and can also be reconfigured to decode Turbo coded data. SOVA is the algorithm implemented for Turbo decoding. The target application is W-LAN, 3GPP and GSM.

A dual mode Viterbi/Turbo decoder is introduced in [4]. The component decoder in this architecture has two modes and some of the modules are shared. In Viterbi mode, and the Log Likelihood Ratio (LLR) processors are turned off. Input symbols are sent from Branch Metrics Unit (BMU) processor to Add Compare Select Unit (ACSU) processor and decoded bits are sent out after tracing back. When in Turbo mode, the decoder works as a Maximum A posteriori Probability (MAP) decoder and only the Trace Back Unit (TBU) is turned off.

A Turbo decoder on a dynamically reconfigurable architecture is introduced in [5]. The decoder is optimized for FPGA. The key power-saving technique in this design is the use of decoder run-time dynamic reconfiguration in response to variations in the channel conditions. If less favorable channel conditions are detected, a more powerful, less power-efficient decoder is swapped into the FPGA hardware to maintain a fixed bit error rate.

A custom architecture for FEC coding of 3G is introduced in [6]. It is based on a unified Viterbi/Turbo processing architecture and exploits the common trellis processing operations of two decoding algorithms providing 3GPP compliant decoding to the base station.

Several custom implementation of single mode Viterbi or Turbo decoders have been published in the past (e.g. [7],[8]).

Following key features are not effectively supported by above mentioned and similar related contributions and are in fact the design criteria of RECFEC:

- Programmability: Conventional designs are programmable only to the extent

of few parameters needed to support a very small set of wireless standards.

An example is using a limited number of polynomials for constituent

encoders or supporting a few different sizes for data blocks within a Viterbi

decoder.

- *Flexibility:* Only one or two FEC coding algorithms (e.g. Viterbi/Turbo or LDPC/Turbo) are integrated in related works.

- Scalability: The conventional implementations typically require major hardware modification to accommodate higher data rates or improved performance.

- Choice of algorithm: For every coding scheme, only one algorithm is selected and implemented. For example, SOVA algorithm in [3] or MAP algorithm in [4] is implemented for Turbo decoding.

- Precision: Data paths are fixed and tailored to the required precision.

Modifying the data paths to improve the precision results in significant design changes. For example, 4-bit soft values are used for decoder inputs of Viterbi decoder.

- *Performance:* Modifying an algorithm to improve the performance or using a set of different algorithms depending on the channel quality, data rate, power consumption, etc is not allowed.

- Multiple standards and Emerging algorithms: The conventional approach limits us to a few standards. For a multi-standard platform, none of those designs could cover multiple wireless air interfaces or emerging algorithms without major hardware modifications.

- *Upgradeability:* Being able to upgrade a coding engine via software and even on-the-fly is an appealing feature that can not be achieved in related works.

Having in mind the aforementioned features of an ideal architecture, RECFEC is built on a reconfigurable processor design methodology to make it a multi-standard instruction-level programmable FEC engine.

#### 3 RECFEC Architecture

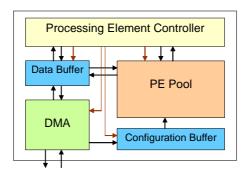

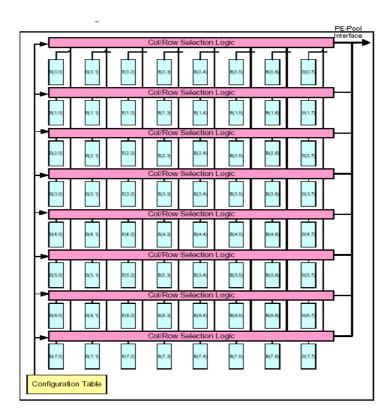

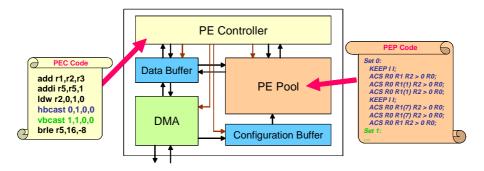

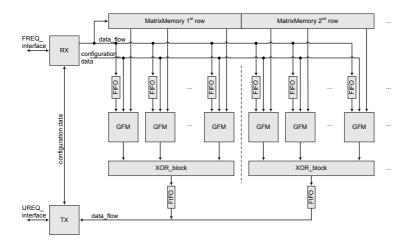

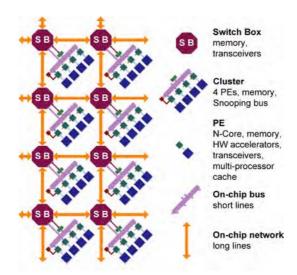

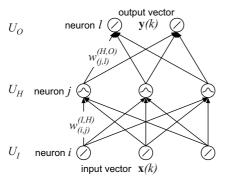

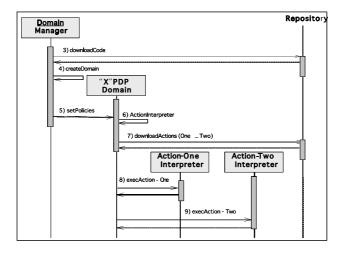

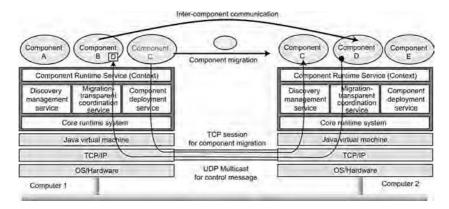

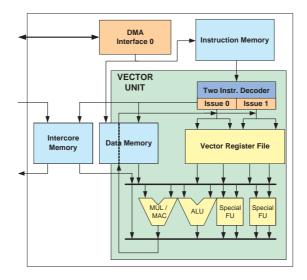

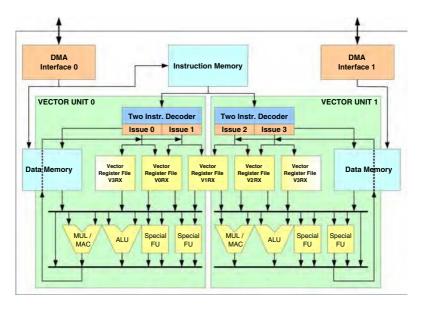

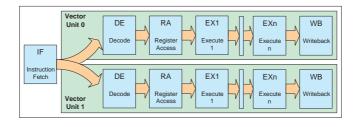

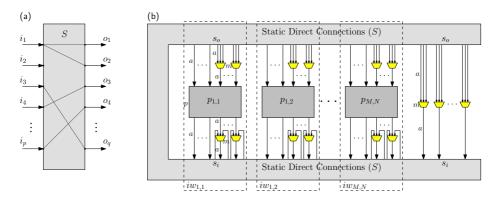

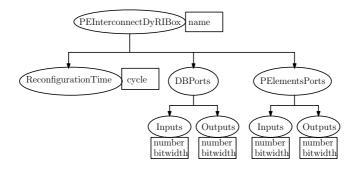

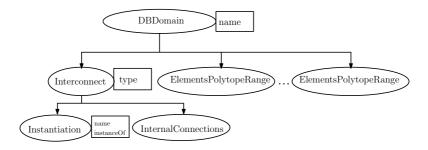

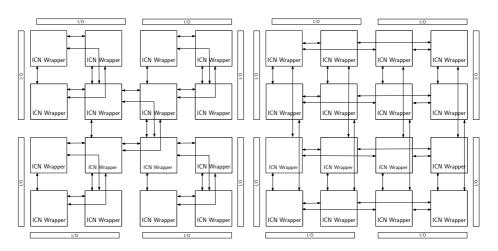

RECFEC architecture is comprised of a parallel array of Processing Elements (PE) controlled by a controller. Fig. 1 demonstrates the architecture of RECFEC. The PE Pool is a two dimensional array of Processing Elements performing parallel

Fig. 1. RECFEC architecture

execution of instructions, which are called *Configurations*. Data and Configuration information are stored in the *Data Buffer* (DB) and the *Configuration Buffer* (CB).

During the execution, *Configuration Words* which accommodate the configuration information of PEs are broadcast from the CB to the PE Pool and are stored in *Configuration Registers*. DB is embedded data memory that interfaces with external memory pumps data to the PE Pool. The high throughput data network facilitates the supply of data to and collection of the results from the PE Pool. Reconfiguration of the network connecting the DB to the PE Pool facilitates the support of different data movement patterns. All data transfers between the DB or the CB and the external memory are handled by the *DMA Controller*. The *PE Controller* is a general purpose 32-bit RISC processor which controls the sequence of operations. In following sections, components of this architecture are elaborated upon.

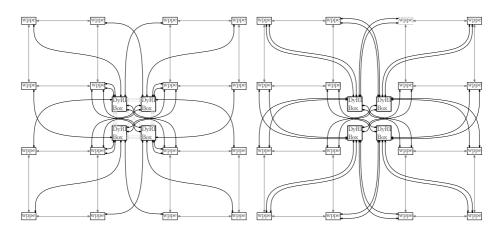

#### 3.1 Processing Elements Pool

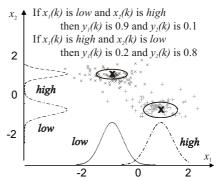

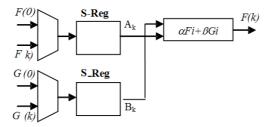

The PE Pool is an array of reconfigurable processing elements. Considering the implementation of FEC algorithms, PE Pool is organized as an 8x8 array of PEs. The PE Pool follows the *SIMD* model of computation. All PEs in the same row/column share the same Configuration Word. However, each PE operates on different data. Sharing the configuration across a row/column is useful for data-parallel FEC algorithms. The PE Pool has a mesh interconnection network, designed to enable fast data exchange between PEs. Each PE encapsulates four 8-bit functional units, as shown in Fig. 2:

- *ALU*: The Arithmetic Logic Unit (ALU) is designed to implement basic logic and arithmetic functions. The functionality of the ALU is configured through control bits. These control signals are generated by the PE decoder based on the information in the Configuration Register

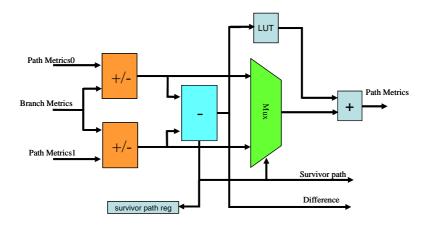

- Add, Compare and Select (ACS) unit: This unit performs ACS, Max and Max\*

operations required in Viterbi and Turbo coding. In the Viterbi algorithm,

branch metrics are updated using following equation:

$$PM_{i',t+1} = Min(PM_{i,t} + BM_{ii'}, PM_{j,t} + BM_{ji'})$$

(1)

where PM and BM represent the path metrics and branch metrics of a trellis butterfly as shown in Fig. 3. This operation is performed in a single cycle using the dedicated ACS unit shown in Fig. 4. The unit is also capable of calculating Max and Max\* operations which are frequently used in Turbo coding:

$$Max^*(x,y) = Max(x,y) + log(1 + e^{-|y-x|}) = Max(x,y) + f_c(|y-x|)$$

(2)

where  $f_c(.)$  is the correction factor that could be implemented using the integrated lookup table in ACS unit.

- GF Accelerator: The Galois Field accelerator is a dedicated engine that

performs modulo and modulo multiply operations used in Reed-Solomon

decoding [9]. Modulo add instruction is implemented using the XOR

integrated in ALU.

- *Lookup Table*: It is a 16-byte local memory in PEs used for lookup table and temporary storage.

Fig. 2. Processing element architecture

Fig. 3. Trellis butterfly

Fig. 4. ACS Unit

#### 3.2 Data Buffer

The Data Buffer (DB) is an important component of RECFEC which is analogous to a data cache. It makes memory accesses transparent to the PE Pool by overlapping of computation with data loading and storage. It is designed as a dual port memory which facilitates the simultaneous access by two different resources, e.g. the PE Controller, the PE Pool and the DMA.

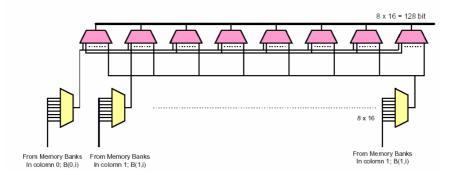

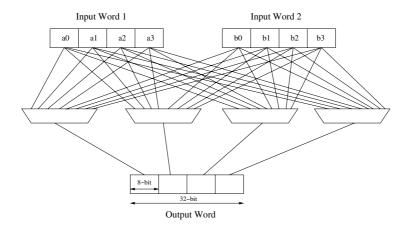

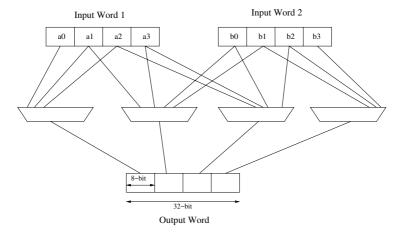

The Data Buffer consists of 64 memory banks where each bank is associated with one PE in the PE Pool and feeds it with one byte per clock cycle. A DB bank is a set of memory segments. Normally, during each access 64 banks are activated which provide 64×8 bits of data for PE Pool with the memory organized into multiple 512-bit lines. The DB supports 16, 32 and 64-bit accesses as well. Fig. 5 illustrates the Data Buffer. In order to enable a variety of permutations a selection logic network is integrated into the DB. The network pattern is determined by providing the right configuration for the Configuration Table which in turn sends appropriate control signals to the selection logic network as shown in Fig. 6. Eight selection logic networks are integrated to address 8 rows. Every selection logic network provides the data for 8 PEs. By employing two levels of multiplexers every PE is able to access any bank in the DB. This feature facilitates random permutation, interleaving and data shuffling. Consequently, the design of PE Pool interconnection network is relaxed and complicated data movement is handled by selection logic in the DB.

#### 3.3 Configuration Buffer

The Configuration Buffer (CB) stores the configuration program of the PE Pool. The Configuration Program is the list of instructions (Configuration Words) of every PE including the operation and its sources and destination. Configuration Words are 32 bits each. In every cycle, Configuration Words of PEs are broadcast to the PE Pool and stored in the Configuration Registers of the PEs. Broadcast patterns can be horizontal or vertical. In horizontal/vertical mode, all PEs in the same row/column

Fig. 5. Data Buffer organization

shares the same Configuration Word and perform the same operations on different input data (SIMD). Furthermore, Configuration Words can initially be stored in the Configuration Registers of the PEs. Later, the PEs can execute the stored Configuration Words repeatedly (MIMD).

#### 3.4 PE Controller

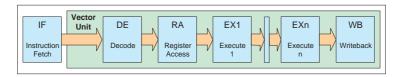

The PE Controller is a 32-bit MIPS-like RISC processor with a four stage pipeline which orchestrates the operation of the PE Pool. It includes sixteen 32-bit registers and three functional units, a 32-bit ALU, a 32-bit shift unit and a memory unit as well as a 4-state pipeline. The instruction set of this RISC processor is augmented with special instructions to control the PE Pool. The RISC processor works at 250MHz.

#### 3.5 DMA Controller

The DMA controller is programmed to transfer data and Configuration Words to the DB and the CB. The PE Controller commands the DMA controller to bring the

Fig. 6. Row/column selection logic in Data Buffer

Configuration Words to Configuration Memory. Once the Configuration Words are in place, they can be broadcast to the PE Pool. It also instructs the DMA to bring the raw data for decoding from external memory to the DB. Once the decoding is done on a block of data, the DMA sends it out to external memory.

#### 3.6 Interconnection Network

A mesh design is chosen for the interconnection network. Every PE is connected to 4 neighboring PEs: top, bottom, right and left. Therefore PEs can share their internal registers with adjacent ones. On the other hand, data communication between non-adjacent PEs is handled via the DB. In many algorithms, high speed data movement happens between adjacent PEs. For example, ACS inputs in Viterbi or Turbo will be originated from neighboring cells which will be performed in single cycle. In this case mesh network could effectively support this type of traffic. For more complicated patterns, data is written to the DB and reordered while reading back to the PE Pool. This will require an extra cycle.

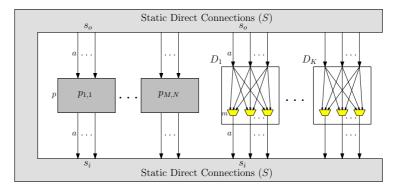

## 3.7 Programming Model of RECFEC

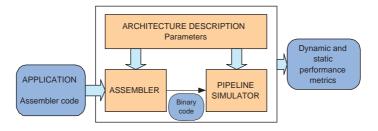

In RECFEC, FEC algorithms can be implemented in software. An algorithm is partitioned into two segments: *control segment* and *processing segment*. In FEC algorithms, the processing segment is usually very parallel and is mapped to the PE Pool. There are some control and scheduling parts in algorithms that are handled by the PE Controller. A RECFEC program consists of two sections: *PE Controller Code* (*PEC Code*) is the main control and scheduling program that orchestrates the operation of the PE Pool, the Data Buffer, the DMA and the Configuration Buffer. *PE Pool Code* (*PEP Code*) is the parallel Configuration Words for PEs. Configuration Words are broadcast to PE Pool using special instructions in PEC Code pointing to corresponding Configuration Words in PEP Code. The programming model of RECFEC is illustrated in Fig. 7.

Fig. 7. Programming model

# 4 Implementation of FEC Algorithms

In this section we present an example of implementation of the Viterbi and Turbo algorithms on RECFEC.

## 4.1 The Viterbi Algorithm

The Viterbi decoder [10],[11] is employed in many different wired and wireless applications ranging from disk drives to W-LAN, W-CDMA, WiMAX and DVB-H.

In order to utilize the maximum parallelism of the Viterbi algorithm, an efficient mapping approach is of great importance. A systolic implementation on a reconfigurable SIMD architecture is shown in [12]. However due to the interconnection network of the PE Pool and between the PE Pool and the DB, a parallel implementation has a better performance on RECFEC. The Viterbi decoder used in W-LAN has the constraint length K=7 which corresponds with 64 trellis states. By assigning one state to every PE, 64 parallel trellis states are mapped to 64 PEs. Following steps summarize the algorithm:

- Branch metrics calculation: Branch metrics are calculated in parallel in all 64 PEs. The 4-bit soft value symbols are stored in the DB. 128 symbols are broadcast to the PE Pool. Every PE reads two symbols and calculates appropriate branch metrics. Four branch metrics are required per trellis stage. Two of them are calculated. By changing their signs, other two branch metrics are generated.

- *Path metrics calculation:* ACS is the main instruction in this step. 64 PEs perform 64 parallel ACS operations in every cycle. Path metrics are updated and then stored back to the DB.

- Survivor paths storage: Survivor paths are represented by single bit flag of ACS instruction and stored in the DB to be used for Trace Back.

- *Trace back:* Due to the sequential nature of trace back, it is performed on the PE Controller. The PE Pool is disabled in this step.

Fig. 8 shows the processing schedule of the Viterbi decoder and the mapping of trellis diagram to the PE Pool as performed on RECFEC. This mapping is applicable for the Viterbi decoder used in W-LAN which has 64 states.

In W-CDMA, the coder has constraint length 9 which results 256 trellis states. One efficient mapping is to allocate 4 adjacent states to one PE. Therefore every PE performs 4 back-to-back ACS operations. This mapping requires 4 internal registers to store the path metrics. Another mapping scenario is to use half of the PE Pool for the trellis and consequently ACS operations of 8 states are performed sequentially in every PE. The other half of the PE Pool can be used then to perform similar operations, but on a different Viterbi block. As a result two encoded blocks will be decoded concurrently. The problem with this approach is the latency and the availability of parallel blocks. We summarized the performance of the single block implementation of Viterbi in Table 1. The maximum throughput in this approach is good enough for W-LAN application. For W-CDMA, the maximum throughput is much more than mandated date rate. In W-CDMA standard, Viterbi algorithm is only used for low data rate voice and not for high speed data (HSDPA).

Fig. 8. a. Processing schedule of the Viterbi algorithm, b. Trellis butterflies mapped to PEs

|   | K | R   | Brach Metrics<br>Calculation<br>(cc/bit) | Path Metrics<br>Calculation<br>(cc/bit) | Survivor<br>Path Storage<br>(cc/bit) | Trace<br>Back<br>(cc/bit) | Total<br>(cc/bit) | Mbps  |

|---|---|-----|------------------------------------------|-----------------------------------------|--------------------------------------|---------------------------|-------------------|-------|

| Ī | 7 | 1/2 | 0.03                                     | 3                                       | 1.06                                 | 0.42                      | 4.51              | 55.43 |

| Ī | 7 | 1/3 | 0.05                                     | 3                                       | 1.06                                 | 0.42                      | 4.53              | 55.24 |

| Ī | 9 | 1/2 | 0.03                                     | 12                                      | 4.25                                 | 0.63                      | 16.91             | 14.79 |

| Π | 9 | 1/3 | 0.05                                     | 12                                      | 4.25                                 | 0.63                      | 16.92             | 14.77 |

Table 1. Performance of the Viterbi decoder implementation

## 4.2 Turbo Algorithm

By using iterative techniques, Turbo decoders [13] provide large coding gains and are widely used in digital communication standards like W-CDMA, HSDPA, WiMAX as well as satellite and deep-space communications.

An iteration of Turbo decoder consists of two Soft Input Soft Output (SISO) decoders corresponding to the encoder network which provide a measure of reliability of the decoded bits. There are two types of soft decision decoding algorithms which are typically used, the first being a modified Viterbi algorithm which produces soft outputs and hence is called a soft output Viterbi algorithm (SOVA) [14]. A second algorithm is the maximum *a posteriori* (MAP) algorithm [15, 16] which results a better performance especially in low SNR conditions with the penalty of higher computational complexity. Log-MAP which simplifies the MAP algorithm computation by taking that to log domain and its approximation, MAX-Log-MAP are typically used in hardware implementation [17, 18].

RECFEC supports the implementation of either of these algorithms in software. As shown in Fig. 3, a powerful ACS unit is embedded in PEs which can perform MAX or MAX\* operations. It can also generate the difference of path metrics to be used in soft Viterbi implementation.

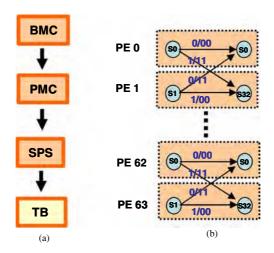

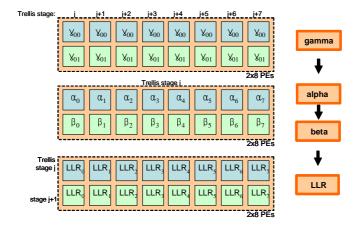

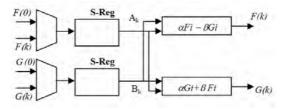

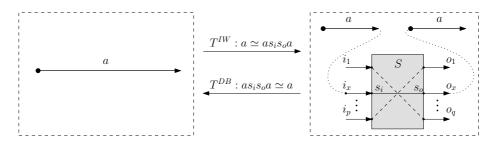

The Turbo decoder in W-CDMA has 8 states. Two rows of the PE Pool are effectively utilized to implement a Turbo decoder. A MAX-LOG-MAP implementation requires the mapping of four major functions of a SISO decoder:

- Gamma calculation: It is similar to branch metrics calculation in the Viterbi algorithm. 4 γ values are required for every trellis stage: γ<sub>00</sub>, γ<sub>01</sub>, γ<sub>10</sub>, γ<sub>11</sub>. Two values are calculated and the other two are derived by changing the sign of the first two values. 8 PEs in the first row and the second row calculate γ<sub>00</sub> and γ<sub>01</sub> of 8 trellis stages respectively in 6 cycles. The state assignment to the PEs is shown in Fig. 9.

- Alpha calculation: Using the ACS accelerator, MAX\* operation which is the main operation of α and β calculations is performed effectively on PEs. 8 PEs on the first row is allocated to handle α calculation of 8 states of a trellis stage in 4 cycles.

- *Beta calculation:* It is similar to alpha calculation and is mapped to the second row of PEs and is performed concurrently with α calculation.

Fig. 9. Mapping of a Turbo decoder on PEs

Log Likelihood Ratio (LLR) calculation: This step requires reading of α, β and γ of

all states and computation of log likelihood which is add, subtract and comparison.

Once LLR values of all states are compared, the maximum is selected. Two

rows perform the LLR computation of two separate stages in 9 cycles.

Fig. 9 shows the mapping of  $\alpha$ ,  $\beta$  and  $\gamma$  calculations. Interleaving function is performed by programming the customized pattern to the Configuration Table of the DB. Hard decision bits are generated after the final iteration on two rows.

Multiple levels of parallelism in a Turbo decoder can be address by this mapping using the PE Pool: *SISO level* (multiple blocks in two concurrent SISO decoders), *Decoder level* (multiple SISO decoders) and System *level* (multiple decoders to process parallel FEC blocks).

Table 2 captures the performance of a Turbo decoder used for W-CDMA on a 3856- bit block using MAX-LOG-MAP algorithm.

|   |     |      | SISO | Decode | r (cc/dec/ | bit)      |                           |                     |                    |

|---|-----|------|------|--------|------------|-----------|---------------------------|---------------------|--------------------|

| K | R   | γ    | α    | β      | LLR        | Int/Deint | Hard Decision<br>(cc/bit) | Total (cc/bit/iter) | Mbps<br>(per iter) |

| 4 | 1/3 | 0.75 | 2    | 2      | 4.50       | 0.50      | 0.38                      | 19.58               | 51.09              |

**Table 2.** Performance of the Turbo decoder implementation

# 5 Conclusion

In this paper, a novel reconfigurable processor is introduced that is optimized for forward error correction. The architecture is parallel and flexible and compared to conventional implementation of FEC decoders, it is instruction-level programmable and can accommodate multiple implementations of FEC algorithms. The architecture can efficiently host evolving algorithms or multiple algorithms for the same coding scheme and enables adaptive choice of algorithms in different situations. A mapping scenario of Viterbi and Turbo coding is presented as a case study and performance metrics are presented.

# References

- A.J Viterbi, "Wireless digital communication: a view based on three lessons learned," IEEE Com. magazine, Vol. 29, pp 33-36, Sep. 1991.

- S. Halter, M.Oberg, P.M. Chau, P.H.Siegel, "Reconfigurable signal processor for channel coding and decoding in low SNR wireless communications," IEEE workshop on signal processing systems, pp. 260-274, 1998.

- 3. J.R. Cavallaro, M. Vaya, "VITURBO: a reconfigurable architecture for Viterbi and turbo decoding," in proceedings of ICASSP '03, Vol. 2, pp. 497-500, 2003

- 4. K. Huang, F.M. Li, P.L. Shen, A.Y. Wu, "VLSI design of dual mode Viterbi/Turbo decoder for 3GPP," in proceedings of ICAS '04, Vol. 2, pp. 773-776, 2004.

- J. Liang, R. Tessier, D. Goeckel, "A dynamically-reconfigurable, power-efficient Turbo decoder," in proceedings of 12th Annual IEEE Symposium on Field-Programmable Custom Computing Machines, pp. 91-100, 2004.

- C. Thomas, M.A. Bickerstaff, L.M. Davis, T. Prokop, B. Widdup, G. Zhou, D. Garrett, C. Nicol, "Integrated circuits for channel coding in 3G cellular mobile wireless systems," IEEE Com. Magazine, Vol. 41, pp. 150-159, Aug. 2003.

- J. Ertel, J. Vogt, A. Finger, "A high throughput Turbo Decoder for an OFDM-based WLAN demonstrator," in proceedings of 5th International ITG Conference on Source and Channel Coding (SCC), Jan. 2004.

- 8. A.J. Viterbi, "An intuitive justification and a simplified implementation of the map decoder for convolutional codes," IEEE Journal on Selected Areas in Communications, Vol. 16, pp. 260-264, Feb. 1998.

- J. H. Lee, J. Lee, M. H. Sunwoo, "Design of application-specific instructions and hardware accelerator for Reed-Solomon codecs," EURASIP Journal on Applied Signal Processing, Vol 2003, pp 1346-1354, 2003.

- 10. A. Viterbi, "Error bounds for convolutional coding and an asymptotically optimum decoding algorithm," IEEE Trans. Info. Theory, Vol. IT-13, pp. 260-269, Apr. 1967.

- G.D. Forney, "The Viterbi algorithm," in proceedings of the IEEE, Vol. 61, pp.268-278, Mar. 1973.

- 12. A. Niktash, H. Parizi, N. Bagherzadeh, "A Multi-standard Viterbi Decoder for mobile applications using a reconfigurable architecture," in proceedings of VTC, Fall 2006.

- 13. C. Berrou, A. Glavieux, P. Thitimajshima, "Near Shannon limit error-correcting coding and decoding: Turbo codes," in proceedings of ICC '93, pp. 1064-1070, 1993.

- 14. J. Hagenauer, P. Hoeher, "A Viterbi algorithm with soft-decision outputs and its applications," in proceedings of GLOBECOM '89, pp. 1680-1686, 1989.

- L. R. Bahl, J. Cocke, F. Jelinek, J. Raviv, "Optimal decoding of linear codes for minimizing symbol error rate," IEEE Trans. Info. Theory, Vol. 20, pp. 284-287, Mar. 1974.

- 16. S. Pietrobon, S. A. Barbulescu, "A simplification of the modified Bahl decoding Algorithm for systematic convolutional codes," Int. Symp. Info. Theory and its Applications, pp. 1073–1077, Nov. 1994.

- 17. J. A. Erfanian, S. Pasupathy, G. Gulak, "Reduced complexity symbol detectors with parallel structures for ISI channels," IEEE Trans. on Com., Vol. 42, pp. 1661-1671, 1994.

- W. Koch, A. Baier, "Optimum and sub-optimum detection of coded data disturbed by time-varying inter-symbol interference," in proceedings of GLOBECOM '90, pp. 1679-1684, Dec. 1990.

# FPGA-Accelerated Deletion-Tolerant Coding for Reliable Distributed Storage

Peter Sobe and Volker Hampel

University of Luebeck

Institute of Computer Engineering

{sobe, hampel}@iti.uni-luebeck.de

Abstract. Distributed storage systems often have to guarantee data availability despite of failures or temporal downtimes of storage nodes. For this purpose, a deletion-tolerant code is applied that allows to reconstruct missing parts in a codeword, i.e. to tolerate a distinct number of failures. The Reed/Solomon (R/S) code is the most general deletion-tolerant code and can be adapted to a required number of tolerable failures. In terms of its least information overhead, R/S is optimal, but it consumes significantly more computation power than parity-based codes. Reconfigurable hardware can be employed for particular operations in finite fields for R/S coding by specialized arithmetics, so that the higher computation effort is compensated by faster and parallel operations. We present architectures for an application—specific acceleration by FPGAs. In this paper, strategies for an efficient communication with the accelerating FPGA and a performance comparison between a pure software-based solution and the accelerated system are provided.

## 1 Introduction

Distributed and parallel computations require globally accessible, fast and reliable storage. To avoid bottlenecks and to overcome the relatively low performance of single magnetic disks, storage architectures serving these requirements are distributed systems itself. The basis technique is to parallelize storage activities on a group of storage units in combination with a striping layout of the data. Storage systems that make use of this principle by software—based layers are, for example, PVFS2[5], Lustre[6] and NetRAID[8]. Fault-tolerant codes take benefit from the striping layout by providing check information across many storage resources that allows to tolerate the loss of storage units. Performance and the degree of fault-tolerance provided by a code usually underlie a tradeoff, i.e. improving reliability increases computation effort for coding which slows down access rates. This tradeoff can get mitigated by parallelizing coding on a proper hardware architecture. FPGAs can be such a platform for parallel coding. This is motivated by the recent advances in this technology that have resulted in powerful devices with reasonable high clock rate and a high number of logic blocks. Recently, FPGAs have been integrated in pioneer High Performance Computer (HPC) systems, such as the Cray XD1. These systems distinguish from others by a closer connection of CPUs and FPGAs, which allows low latency and high bandwidth communication. When FPGAs are configured as customized coprocessors, particular applications may gain an execution acceleration of 20 to 100, yet, achieving these values proofs to be non-trivial. The presented work is based on the NetRAID [8,9] storage system that is designed for cluster systems with distributed memory and local disks. If available, FPGAs can be interfaced to speed up R/S coding. The experiments documented in this paper were run on a Cray-XD1 machine, equipped with Xilinx Virtex 4 FPGAs.

The paper is structured as follows. In Section 2, a distributed storage system is introduced with a focus on redundancy coding together with a preliminary estimation of the acceleration gain. Accelerator designs, beginning with a FPGA-based Galois Field (GF) multiplier array and yielding to an architecture of a R/S coprocessor are explained in Section 3, followed by an experimental performance evaluation in Section 4. A section positioning the presented work within related research concludes the paper.

# 2 Distributed Reliable Storage

#### 2.1 Overview

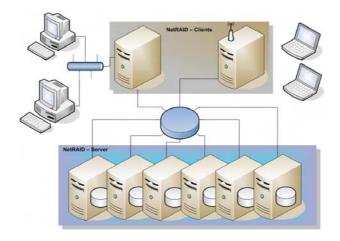

A software-based distributed storage system, called NetRAID is used to compare the pure software approach with an FPGA-accelerated one. In NetRAID, a group of storage servers establish parallel access to data. Fig. 1 illustrates for example a group of 6 servers, accessed by 2 clients. Data is striped across Nservers, additionally M servers can be configured to store redundancy. For the depicted example, parameters (N,M) would be (5,1) for a parity code, and (4,2) for a R/S code, the latter with the ability to tolerate two failed storage devices. The computations for encoding and decoding are completely done by the clients that use a library for file system access. Alternatively, an integration into a filesystem is reached using a FUSE-based daemon. Together with several variants of parity-based codes, a Reed/Solomon code according to [2,3] is integrated. By data striping and parallel storage activity, the access bandwidth to data is improved significantly. Ideally, the bandwidth can be scaled with the number of storage servers until the network capacity is saturated. Practically, 8 to 16 storage devices work efficiently in parallel. Access rates up to 280 MByte/s were measured for a single client process and up to 640 MByte/s for collective access by many clients to a set of 16 storage servers, both without applying any redundancy codes. Redundancy codes slow down access (a) when data is written and (b) when data is read from a storage system containing a single or a few failed storage devices. Still a good performance is achieved by parity-based codes. Operations for en- and decoding are bit-wise XORs of 32/64 Bit operands that are properly supported in all common microprocessors. The situation changes when Reed/Solomon (R/S) codes have to be calculated on common microprocessors. The arithmetics necessary for R/S are not supported by instructions directly and thus require complex and time-consuming calculations.

Fig. 1. The NetRAID storage system

## 2.2 Reed/Solomon Coding

Conceptually, the creation of N + M data words and check words (the redundancy) to store on N + M locations is done by multiplying a constant matrix A with the vector D that consists of N data words:

$$AD = E,$$

$A = \begin{bmatrix} I \\ G_{sub} \end{bmatrix}, E = \begin{bmatrix} D \\ B \end{bmatrix}$  (1)

where I represents the  $(N \times N)$ -identity-matrix,  $G_{sub}$  is a sub-matrix of the code generator matrix. The structure of the generator matrix guarantees the invertibility when any M rows get discarded from A. The result vector E contains the check words in B, with M check words. For encoding, solely redundancy has to be calculated, dropping the part of the equation system related to the identity matrix. The check words are calculated word-wise as a linear combination of N data words and factors, as expressed by equation (2), where  $b_i$  (i = 1, ..., M) are the words on the i-th storage unit among the M redundant ones,  $d_j$  (j = 1, ..., N) denote original data words on a data storage unit j. The factors  $g_{ij}$  are elements of a  $(M \times N)$  matrix  $G_{sub}$ .

$$b_i = \sum_{j=1}^{N} d_j g_{ij}.$$

(2)

R/S is able to recover up to M failures at all. If an error occurs, the missing elements of vector D can be recalculated by using data at the non faulty storage devices. E' represents the vector with at least N remaining words and A' is the subset of N rows of A belonging to the non faulty elements in E'. The data vector can be recovered with help of the matrix-vector multiplication:

$$D = A^{'-1}E' \tag{3}$$

A' and E' can be taken directly from A and E by omitting the rows/elements that correspond to failed storage devices. The inverse  $A'^{-1}$  is calculated once after fault detection. Later on, all missing data words can be reproduced by computing the missed elements in D according to formula (3).

This approach, based on a linear equation system, requires Galois Field (GF) arithmetics for an exact reproduction of missed data. Integer and floating point operations are not capable of an exact recovery, due to the inability to operate within a finite value range and due to rounding errors, respectively. The word size of GF elements depends on the field used, n=8 for GF(2<sup>8</sup>) fits well to practical system sizes and leads to elements that can be addressed in a Byte–aligned way.

Practically, redundancy is calculated by multiplying a word from each storage device with a constant taken from  $G_{sub}$ . After that, the products have to be added, which fortunately maps to the XOR operation in the Galois Field. This leads to N multiplications and N-1 additions in GF arithmetics. The number of operations is dedicated to a single word on a single redundancy storage. Thus, the N GF-multiplications and N-1 XORs must be executed M times each, as  $M \geq 2$ . The effort as number of operations is summarized in Table 1 for parity, R/S and for a computationally optimal MDS code, which is available only for a few special cases (e.g. Evenodd [1] with M=2). Maximum distance separable codes[4] (MDS) allow to tolerate any M failures with M additional storage devices, such as R/S.

$\begin{array}{|c|c|c|c|c|} \hline & XOR & GF-Mult \\ \hline Parity (M=1) & N-1 & 0 \\ \hline R/S & M\times (N-1) & M\times N \\ \hline optimal & M\times (N-1) & 0 \\ \hline \end{array}$

Table 1. Computation effort in number of operations

As expected, Reed/Solomon codes are expensive in terms of computation cost. This coding effort appears for the write operation, because data is to encode always, even on a group of fault free storage units. The read operation is still fast for a fault free system, but the access rate drops to a few ten MByte/s in case of a storage group with failed units. Particularly, the slow write access is an undesired effect for applications that have to rely on fault-tolerant data storage. A detailed performance analysis can be found in [9], where for example a write rate slowdown of about 50 % for M=2 is reported. R/S coding executed on a hardware-accelerated platform promises to keep up with fast storage access and still to achieve the fault-tolerance properties of a MDS code.

## 2.3 Preliminary Analysis

An analysis shall show, under which system parameters an acceleration by a FPGA will be beneficial. A limiting factor must be seen in the lower clock frequency of the FPGA, thus a frequency factor T is introduced.

$$T = \frac{f_{FPGA}}{f_{CPU}} \tag{4}$$

A microprocessor is able to complete a XOR operation in each clock cycle. An accelerating coprocessor can deliver results of a GF multiplication and further logic operations each clock cycle as well, a pipelined architecture taken into account (see 3.2).

When a software-based execution of a GF multiplication is A times slower than a XOR operation, the coprocessor would do a comparable computation A times faster than software, assumed processor and FPGA would run with the same clock frequency. The effect of the lower FPGA clock rate is taken into account by factor T. This approach allows to measure A by comparing the XOR bandwidth  $(B_{XOR})$  with the GF multiplication bandwidth  $(B_{GFM})$  in the CPU.

$$A = \frac{B_{XOR}}{B_{GFM}} \tag{5}$$

To be comparable, the accelerated R/S encoding includes GF products on a number of operand pairs, filling the word size of the processor (32/64 Bit). Additionally, subsequent XOR operations to add the products can get easily included. Thus, more functions are provided by the accelerator compared to a single instruction on the CPU. The factor A' extends A by expressing these additional computations. N multiplications and N-1 XOR operations provided by the coprocessor have to be set into relation with N-1 XOR operations that would be calculated by software for a computationally optimal MDS code.

$$A' = \frac{A \cdot N + (N-1)}{N-1} \tag{6}$$

With the following criterion,

$$S = T \times A' \tag{7}$$

the speedup is quantified. Acceleration by a FPGA is worth when S is significantly larger than one. Experiments on a Cray XD1 node let us measure the calculation rates and determine  $T=200 {\rm MHz}/2200 {\rm MHz}=0.\overline{09}$ . The results shown in Table 2 demonstrate that an acceleration related to software-based R/S can be achieved.

Table 2. Calculation bandwidth (MByte/s) for XOR and GF-multiplications

| block size | $B_{XOR}$ | $B_{GFM}$ | A    | A' for $N=8$ | S    |

|------------|-----------|-----------|------|--------------|------|

| 512 Byte   | 7721      | 180       | 42.9 | 50.0         | 4.55 |

| 2048 Byte  | 8533      | 182       | 46.9 | 54.6         | 4.96 |

| 8192 Byte  | 8684      | 169       | 51.4 | 59.7         | 5.42 |

# 3 FPGA-Accelerated Reed/Solomon Coding

# 3.1 Cray XD1 Environment

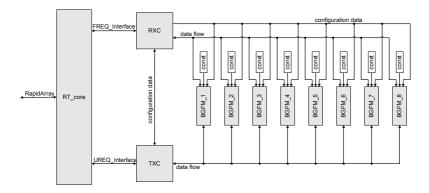

As described in [10], the Cray XD1 is a parallel computer with multiprocessor nodes that can be optionally equipped with several types of Xilinx FPGAs. All communication between CPUs and FPGAs is handled by the Cray RapidArray interconnect that directly interfaces the CPUs via HyperTransport. AMD Opteron CPUs provide a direct access to the HyperTransport, and thus to the RapidArray. For the FPGA logic, appropriate blocks have to be integrated to control the communication via RapidArray. For this purpose Cray provides an intellectual property core to access the RapidArray via two independent communication interfaces for system and FPGA initiated requests, respectively. As the FPGA can be clocked with up to 200 MHz and each of the communication channels being 64 Bits wide, a maximum data rate of 1.6 GB/s per channel can be achieved. The programmed logic in the FPGA is utilized by processes running on the CPUs via an application programming interface provided by Cray. To transfer data from the application into the FPGA, a mapped memory section is used. The FPGA can issue requests to the application as well. To respond to these requests the application must register a memory section to which the FPGA requests are mapped.

# 3.2 Galois Field Multiplier

As a building block, a finite field or Galois Field multiplier (GFM) based upon the Mastrovito Multiplier architecture [11] is implemented in the FPGA logic. The product of two polynomials A(y) and B(y) in  $GF(2^n)$  is calculated using a product matrix Z. This product matrix depends on the polynomial coefficients of the multiplicand and a matrix representation of the field polynomial Q(y), yielding Z = f(A(y), Q(y)). The multiplication is carried out as a matrix-vector multiplication in  $GF(2^n)$  of the product matrix and the multiplier polynomial and thus can be implemented with AND and XOR gates. The whole calculation can be expressed by the following equations:

$$A(y) \cdot B(y) = C(y) \mod Q(y)$$

$$C\left(y\right) = \begin{pmatrix} c_{0} \\ c_{1} \\ \vdots \\ c_{n-1} \end{pmatrix} = Z \cdot B\left(y\right) = \begin{pmatrix} z_{0,0} & \cdots & z_{0,n-1} \\ \vdots & \ddots & \vdots \\ z_{n-1,0} & \cdots & z_{0,n-1} \end{pmatrix} \cdot \begin{pmatrix} b_{0} \\ b_{1} \\ \vdots \\ b_{n-1} \end{pmatrix}$$

This scheme allows to build a highly parallel and pipelined architecture. In the first stage all the coefficients of the product matrix are calculated according to the current field polynomial and the multiplicand. In a second stage, all product matrix rows are multiplied with the multiplier polynomial. Adding the element's

products forms the third stage, and writing the result the fourth. This leads to a latency of four clock cycles for the whole multiplication.

Our implementation is fixed to a width of 8 Bit but variable regarding the finite field to work on. To configure a particular Galois Field, the appropriate matrix representation of the field polynomial can be written to the multiplier.

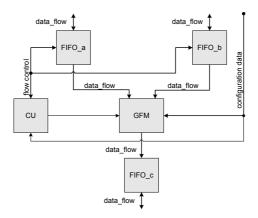

Fig. 2. Block diagram of the buffered Galois Field multiplier (BGFM)

As depicted in Fig. 2, factors are buffered in two separate FIFOs before getting multiplied. Another buffer keeps the results. A control unit synchronizes interactions between all elements, i.e. creates configuration signals and the buffer control signals. The control unit activates the calculation as soon as both input buffers are non-empty and as long as the result buffer is not full.

#### 3.3 GF Multiplier Array

As the RapidArray IP-core can issue one quadword, i.e. 64 bits, per cycle four buffered GF multipliers can work parallel, each with  $2 \times 8$  Bit input width. Doing so completely utilizes the bandwidth provided by the RapidArray. The multiplier array receives the input factors via one communication channel and sends the results via the other. To handle delays or high traffic on the RapidArray, two modules TXC and RXC have been implemented that control the incoming and the outgoing data streams. Based on the signaling of the RapidArray and the filling state of the buffers they may halt and resume communication.

# 3.4 GF Multiplier Array with Implicit Factors (GFMA-IF)

With binding the logic more specifically to R/S encoding and decoding, obviously one factor of each multiplication can be held constant. Thus, one factor of each multiplication must be retrieved from the data flow only, while the other is held fixed in the accelerator. Correspondingly, each clock cycle 64 bits of input data,

eight data words for multiplication, can be processed, using the full capacity of the FPGA's input data bus. These considerations apply to the FPGA's output data bus as well. Each clock cycle eight products are released and have to be returned. The architecture shown in Fig. 3 utilizes eight GF multipliers in parallel.

Fig. 3. Multiplier array with implicit input factors (GFMA-IF)

## 3.5 R/S Coprocessor

In 3.3 and 3.4, two variants of a finite field multiplication acceleration were presented. So far, the algorithms for encoding and decoding still must be executed in software. When moving the R/S coding completely into the FPGA, by combining parallel GF multipliers and XOR logic, the CPU can get completely released from most of the coding operations. The encoding and decoding algorithm, both represented by a matrix-vector multiplication, can be directly translated into a hardware structure. Figure 4 depicts a R/S coprocessor layout of this structure. Data words from N storage units are multiplied with constant factors by N GF-multipliers and summed by a bitwise N-input parity logic. This data path generates a single check word for encoding. Several multiplierparity paths have to be instantiated for multiple check words that are commonly required. Similarly to the GF multiplier array with implicit factors, the computation bandwidth gets fully effective as encoding rate. The code generator matrix  $G_{sub}$  is written to the coprocessor in advance, and hence, the factors do not have to be transferred during coding anymore. Redundancy information is transferred with a lower rate,  $\frac{M}{N}$  of the data input rate. Decoding, which is only necessary when data of failed storage devices has to be reconstructed, is supported by the presented hardware structure as well. For decoding, the matrix memory has to be filled with the rows of  $A'^{-1}$  that correspond to the indexes i of the storages  $d_i$  to reconstruct. The reconstruction requires to fetch N data and redundancy words, to multiply it with the matrix memory values and to sum the products. Up to M data words can be reconstructed by the M parallel data paths.

Fig. 4. Structure of the R/S coprocessor

#### 3.6 Comparison

All the three architectures were synthesized on a XC4VLX160 FPGA with 67584 slices in total. As can be seen from the synthesis results in Table 3, the number of logic cells is not a limiting factor. The multiplier array designs limit the clock speed to 160 MHz and to 115 MHz for the more complex design of the R/S coprocessor. The theoretically reachable transfer bandwidth is determined by the product of clock frequency and the interface width. For the multiplier array, the computed value is only effective by a half, due to the necessity to transfer both factors. The actually reached bandwidth depends on the interaction with the CPUs memory and is slightly lower.

| Design              | Slices used | Clock speed | Theoretical bandwidth (data) |

|---------------------|-------------|-------------|------------------------------|

| GF multiplier array | 8 %         | 160 MHz     | $640~\mathrm{MB/s}$          |

| GF mult. array with | 5 %         | 160 MHz     | 1280  MB/s                   |

| implicit factors    |             |             |                              |

| R/S coprocessor     | 24 %        | 115  MHz    | 920  MB/s                    |

Table 3. Synthesis results

From a functional point of view, the R/S coprocessor embeds most logic functionality in the FPGA and reduces the data stream between CPU and FPGA to a minimum. Each word written to the data storage units is transferred to the FPGA once; and also each check word originated by the coding algorithm traverses the output link from the FPGA to the CPU once. No further processing on the CPU is necessary when the R/S coprocessor is utilized. A drawback of the R/S coprocessor approach is that data is accessed non-contiguously. To

encode a R/S code word, original data must be collected from different positions in the input data that is commonly organized as a linear data structure. The multiplier array with implicit factors (GFMA-IF) corresponds closer to the data structures in a software-based environment. Input data presented in large blocks (e.g.  $6\times24$  kByte) can be transferred sub block-wise (24kByte-wise) to the GFMA-IF and multiplied with a particular factor. The product array must be transfered back to the CPU and there XOR-ed to an array of check words. The GFMA-IF architecture (i) does not embed the entire functionality within the FPGA and (ii) produces more output data than the R/S coprocessor. Despite of these disadvantages, the GFMA-IF architecture with a contiguous data access is still eligible as an accelerator. Eventually, the choice which architecture performs better - the multiplier array with implicit factors or the R/S coprocessor - depends on the granularity of data distribution and on the performance of the memory hierarchy for non-contiguous access.

## 4 Performance Evaluation

In this section we present and discuss the performance of the FPGA-based accelerators. The results are set in relation with the software-based GF multiplication.

#### 4.1 Evaluation Method

For evaluation, the computation bandwidth of the GF multiplication in software as well as for the FPGA-based accelerator has been measured. The FPGA-accelerated variant includes the transfer of data to the logic and the transfer of the results back into the address space of the software process. This process writes a block of factors to the FPGA, where computation of the data starts immediately and the results are written to the transfer region in the memory. Transfer to the FPGA, the processing in the multiplier arrays and the transfer of results back to the memory is fully pipelined. A block-based invocation of the accelerator functionality has been set up to keep allocated memory at reasonable sizes, while large block sizes lead to a sufficient overlap of transfer and communication.

To calculate multiplication rates, the time between writing the first quadword and receiving the last result is taken. In conjunction with the block size in quadwords, different data streams were formed. We chose to run four sessions in which four different amounts of data, being 4 MB, 40 MB, 160 MB, and 640 MB, were multiplied. The block size was varied in each session and the number of iterations was consequently adapted. Each of these combinations of block size and iterations was measured ten times and later analyzed statistically.

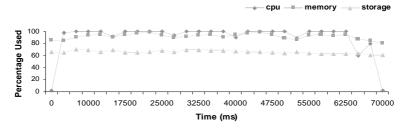

## 4.2 Computation Bandwidth

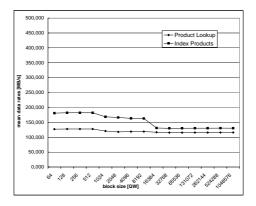

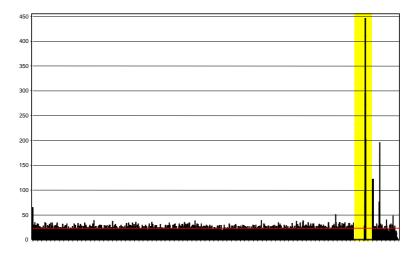

The multiplication rates for the software implementation are shown in Fig. 5. Two software variants have been evaluated - an ordinary product table lookup (Product Lookup) and another product lookup (Index Products) that uses indexes of data and check storages to access a product of a distinct  $g_{i,j}$  with a data word directly. Computation rates of about 130 and 180 MByte/s for each variant were measured. As expected, the indexed lookup performs better. The deviations from the mean values are very small, compared to the FPGA–accelerated GF multiplication.

$\bf Fig.\,5.$  Software  ${\rm GF}(2^8)$  multiplication: Mean throughput (MByte/s) for a varied block size in number of quadwords

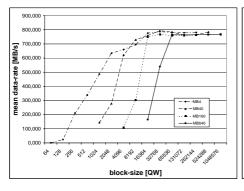

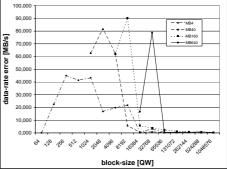

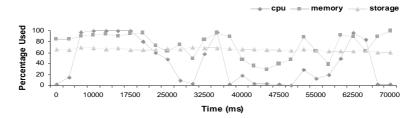

The left part in Fig. 6 shows the mean computation bandwidth, measured for the GF multiplier array with implicit factors (GFMA-IF). Slightly lower mean values, but with very similar progression have been observed for the R/S coprocessor (710 MByte/s maximum instead of 795 MByte/s). The four different plots correspond to the four amounts of data multiplied, the sessions mentioned above. The plot in the right part of Fig. 6 shows the error of the mean values against the block size. It was calculated by dividing the root mean square deviation by the square root of the number of measurements for one combination. When varying the transfer block size in a range from 64 to 32K quadwords, the data rate heavily depends on the block size. With further increasing block sizes, the rate stabilizes at about 800 MByte/s. The threshold block size for fast communication with the FPGA-coprocessor is 16384 quadwords, which equals 128 KByte. The errors of the data rates indicate that the transfer rates fluctuate heavily for small blocks. Errors get very small as soon as a block size of 32768 quadwords is reached, which equals 256 KByte. The achieved computation bandwidth depends on the utilization of both of the buses. An implementation of the architecture can be clocked at 160 MHz. On the input bus a contiguous data stream can be implemented, allowing a maximum transfer rate of 1280 MByte/s. On the output bus a wait cycle has to be implemented after each eight byte block, reducing the maximum transfer rate by 8/9 to 1138 MByte/s. Another aspect is the larger data amount to return in combination with a practically slower output link of the FPGA. We learned from debugging, that communication on the output link

Fig. 6. FPGA-based GFMA-IF: Mean values and errors of the coding throughput

is stalled more frequently than on the input link. The R/S coprocessor is not affected by that slightly lower output rate. The number of results words is M per N input words. Practically, M is less than N and the lower output rate is fully compensated by that.

## 4.3 Insights

From the interpretation of the measured computation rates, three points shall summarize our insights.

- (1) Coarse granular software-accelerator interaction To achieve high data throughput the coprocessor should process blocks of at least 16384 quadwords. In distributed storage systems such block sizes are usual, e.g. 24 KByte per block for striping across eight nodes in NetRAID yields to 24576 quadwords (192 KByte) per invocation of the coding function.

- (2) Estimated speedup has been reached Comparing the hardware–accelerated GF multiplication with the software variant, at least a speedup of four is reached. We compared the fastest software function with the slowest variant of FPGA-accelerated coding on reasonable large blocks. This corresponds to the preliminary estimated speedup in Section 2.

- (3) GFMA-IF and R/S coprocessor are both appropriate solutions The R/S coprocessor and the GFMA-IF architecture both utilize the input bandwidth for GF multiplications fully. The R/S coprocessor adds the products internally and less output data has to be transferred. This compensates a lower transfer rate back to the CPU and releases the memory from traffic. Still a disadvantage is the non-contiguous data access by the R/S coprocessor. Thus, the multiplier array with implicit factors (GFMA-IF) is another proper solution.

## 5 Related Work

Reliable Storage is commonly supported with RAID adapters that work at the  $\rm I/O$  bus level. Except expensive RAID controllers for storage area networks,

there is still a gap between hardware accelerated storage and reliable distributed storage, especially when the storage system is implemented with COTS components. ClusterRAID[7], combines reliable storage with hardware acceleration. The approach is different from NetRAID in the way that data is kept locally on disks. A group of storage nodes, each storing data objects independently, is protected by an erasure–tolerant code. Updates are forwarded to dedicated redundancy nodes that update the redundancy information. ClusterRAID implements a R/S code as suggested in [2]. Acceleration by FPGAs and graphic processors were reported that directly base on logarithm-tables for Galois Field multiplication. A FPGA-based coprocessor is presented in [13], comparable to the GF multiplier array as presented here. The processor does not cover the entire coding data path for R/S; instead it can be configured to perform GF multiplications in a SIMD mode.

GF arithmetic is supported by a few digital signal processors (such as Texas Instruments TMS processors) by simple GF multiplication instructions. Complex GF instructions, such as multiply-add which is often needed for R/S coding, are suggested in [14] for a SIMD implementation in a processor. There are generally numerous systems that implement Galois field arithmetics for error correction in digital communication systems or digital storage with correction of arbitrary Bit corruption and burst errors in the data stream. In comparison, less development is directed to storage systems with an erasure characteristic. For distributed systems, most R/S systems still base on software coding. Despite advances in code construction such as Cauchy R/S codes that allow faster software coding than classical R/S codes, only a few systems make use of specialized hardware. Only recently, FPGAs can be coupled close enough to the CPUs that an acceleration effect can be reached. Today, the trend is visible to add more specific functionality to processors or to provide configurability. In this context our work covers the variant of CPU-FPGA cooperation for fast coding. Other variants of sophisticated coding solutions become feasible, e.g. using configurable coprocessors in parallel on a chip for R/S coding.

#### 6 Conclusion

Sophisticated codes for reliable distributed storage, such as Reed/Solomon, are compute-intense and bound the data access bandwidth. Acceleration by customized logic is a way to reach fast encoding and decoding, keeping up with higher data rates of aggregated storages. The design space, spanning from a Galois Field multiplier array to a R/S coprocessor that covers the entire data path for code word processing has been analyzed. It could be shown that the bandwidth of the FPGA-based accelerator is noticeable higher compared to software coding. The coding bandwidth is bounded by the transfer bandwidth to and from the accelerator. Despite, for the current implementation on a Cray XD1 we could reach a factor four for coding bandwidth acceleration. With such a FGPA acceleration, coding in a distributed data storage architecture is faster than the aggregated storage bandwidth and nearly as fast as high-speed networks.

# References

- Blaum, M., Brady, J., Bruck, J., Menon, J.: EVENODD: An Efficient Scheme for Tolerating Double Disk Failures in RAID Architectures. IEEE Transactions on Computers. Vol. 44, No.2, February 1995

- Plank, J. S.: A Tutorial on Reed-Solomon Coding for Fault-Tolerance in RAID-like Systems. SOFTWARE - PRACTICE AND EXPERIENCE. pp. 995-1012, September 1997

- Plank, J. S., Ding Y.:, Note: Correction to the 1997 Tutorial on Reed-Solomon Coding. Technical Report, University of Tennessee, UT-CS-03-504, April 2003

- 4. Mac Williams, F.J., Sloane, N.J.A.: The Theory of Error-Correcting Codes. Part I, North Holland Publishing Company, Amsterdam, New York, Oakland, 1977

- Carns, P. H., Ligon, W. B., Ross, R. B., Thakur R.: PVFS: A Parallel File System for Linux. Proc. of the 4th Annual Linux Showcase and Conference, pp. 317-327, 2000

- Braam, P.J. et al.: The Lustre Storage Architecture., Cluster File Systems Inc., http://www.lustre.org/docs/lustre.pdf, 2004

- 7. Wiebalck, A., Breuer, P. T., Lindenstruth, V., and Steinbeck, T. M.: Fault-Tolerant Distributed Mass Storage for LHC Computing. CCGrid Conference, 2003

- Sobe, P.: Data Consistent Up- and Downstreaming in a Distributed Storage System. Proceedings of Int. Workshop on Storage Network Architecture and Parallel I/Os, pp. 19-26, IEEE Computer Society, 2003

- Sobe, P. and Peter, K.: Comparison of Redundancy Schemes for Distributed Storage Systems. 5th IEEE International Symposium on Network Computing and Applications, pp 196-203, IEEE Computer Society, 2006

- 10. Cray Inc.: Cray XD1 FPGA Development. Release 1.4 documentation, 2006

- 11. Paar, C.: A New Architecture for a Parallel Finite Field Multiplier with Low Complexity Based on Composite Fields. IEEE Transactions on Computers, Vol. 45, No. 7, pp. 856-861, 1996

- 12. Gilroy, M. and Irvine, J.: RAID 6 Hardware Acceleration. Proc. of the 16th Int. Conference on Field Programmable Logic and Applications 2006, pp. 67-72, 2006

- 13. Lim, W.M. and Benaisse, M.: Design Space Exploration of a Hardware-Software Co-designed  $GF(2^m)$  Galois Field Processor for Forward Error Correction and Cryptography. In: International Symposium on System Synthesis 2003, pp. 53-58, ACM Press, 2003

- Mamidi, S., Iancu, D., Iancu, A., Schulte, M. J. and Glossner, J.: Instruction Set Extensions for Reed-Solomon Encoding and Decoding. Proceedings of the 16th. Int. Conf. on Application-specific Systems, Architecture and Processors (ASAP'05), IEEE, 2005

# LIRAC: Using Live Range Information to Optimize Memory Access

Peng Li<sup>1</sup>, Dongsheng Wang<sup>2</sup>, Haixia Wang<sup>3</sup>, Meijuan Lu<sup>4</sup>, and Weimin Zheng<sup>5</sup>

National Laboratory for Information Science and Technology Research Institute of Information Technology Tsinghua University, Beijing, China {p-li02<sup>1</sup>, lmj<sup>4</sup>}@mails.tsinghua.edu.cn, {wds<sup>2</sup>, hx-wang<sup>3</sup>, zwm-dcs<sup>5</sup>}@tsinghua.edu.cn

Abstract. Processor-memory wall is always the focus of computer architecture research. While existing cache architecture can significantly mitigate the gap between processor and memory, they are not very effective in certain scenarios. For example, when scratch data is cached, it is not necessary to write back modified data. However, existing cache architectures do not provide enough support in distinguishing this kind of situation. Based on this observation, we propose a novel cache architecture called LIve Range Aware Cache (LIRAC). This cache scheme can significantly reduce cache write-backs with minimal hardware support.

The performance of LIRAC is evaluated using trace-driven analysis and simplescalar simulator. We used SPEC CPU 2000 benchmarks and a number of multimedia applications. Simulation results show that LIRAC can eliminate 21% cache write-backs on average and up to 85% in the best case.

The idea of LIRAC can be extended and used in write buffers and CMP with transactional memory. In this paper, we also propose LIve Range Aware BUFfer (LIRABuf). Simulation results show that the improvement of LIRABuf is also significant.

**Keywords:** LIRAC, Live Range, Cache, Write Buffer, Memory Hierarchy.

## 1 Introduction

Processor-memory wall [1] is always one of the most important problems in computer architecture research. While processor follows the well-known Moores law, doubling performance every 18-24 months, the speed of memory access only grows about 7% every year [2]. In the upcoming Chip Multi-Processor (CMP) era, the presence of more processors on a single chip significantly increases the demand of off-chip bandwidth and exacerbates this problem even more.

Modern computers are often equipped with various buffers, such as write-back cache, write buffer and commit buffer in CMP with transactional memory [3][4]. We observe that in computers with buffering technology, actual write operation

P. Lukowicz, L. Thiele, and G. Tröster (Eds.): ARCS 2007, LNCS 4415, pp. 28–42, 2007. © Springer-Verlag Berlin Heidelberg 2007

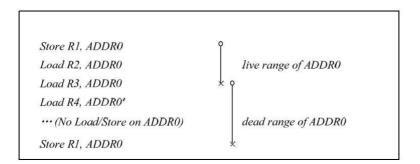

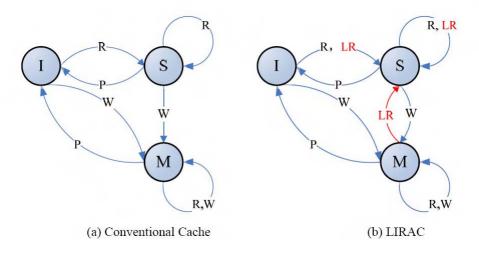

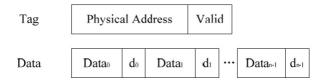

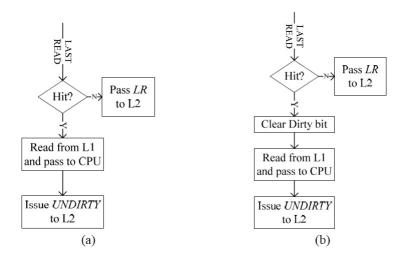

happens after write instruction commitment. By the time memory write operation executes, the data written might already go out of its live range which causes a useless write operation. However, existing buffer architectures cannot effectively take advantage of this observation.

In this paper, we explicitly distinguish writes in processor domain and memory domain, and further propose LIve Range Aware Cache (LIRAC) and Live Range Aware Buffer (LIRABuf). LIRAC and LIRABuf focus on reducing the number of write-back operations, and they do not affect read operations. With write operations decreased, LIRAC and LIRABuf can reduce both execution time and energy.

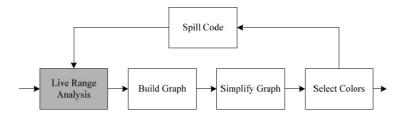

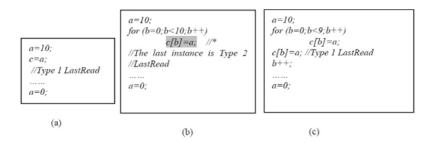

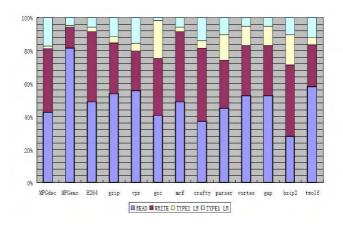

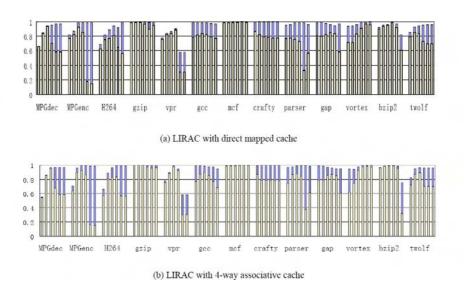

Trace-driven simulations show that LIRAC can reduce 21% write-backs on average and up to 85% in the best case, and LIRABuf can reduce 23% write-backs on average and up to 84% in the best case.